Principal Investigator: Dr. Rob Cuzner

Because the microgrid is a dynamically changing mesh that will respond differently to faults depending on its configuration, achievement of reliable fault discrimination drives complexity and cost. When short circuit faults occur within a microgrid multiple sources of energy can feed the fault, including adjacent electronic loads with front-end filter/storage capacitors–this is particularly the case with DC microgrids where sudden fault inception is characterized only by connected capacitors and cable inductances. An array of additional corner case scenarios exist each of which must be handled in a different way.

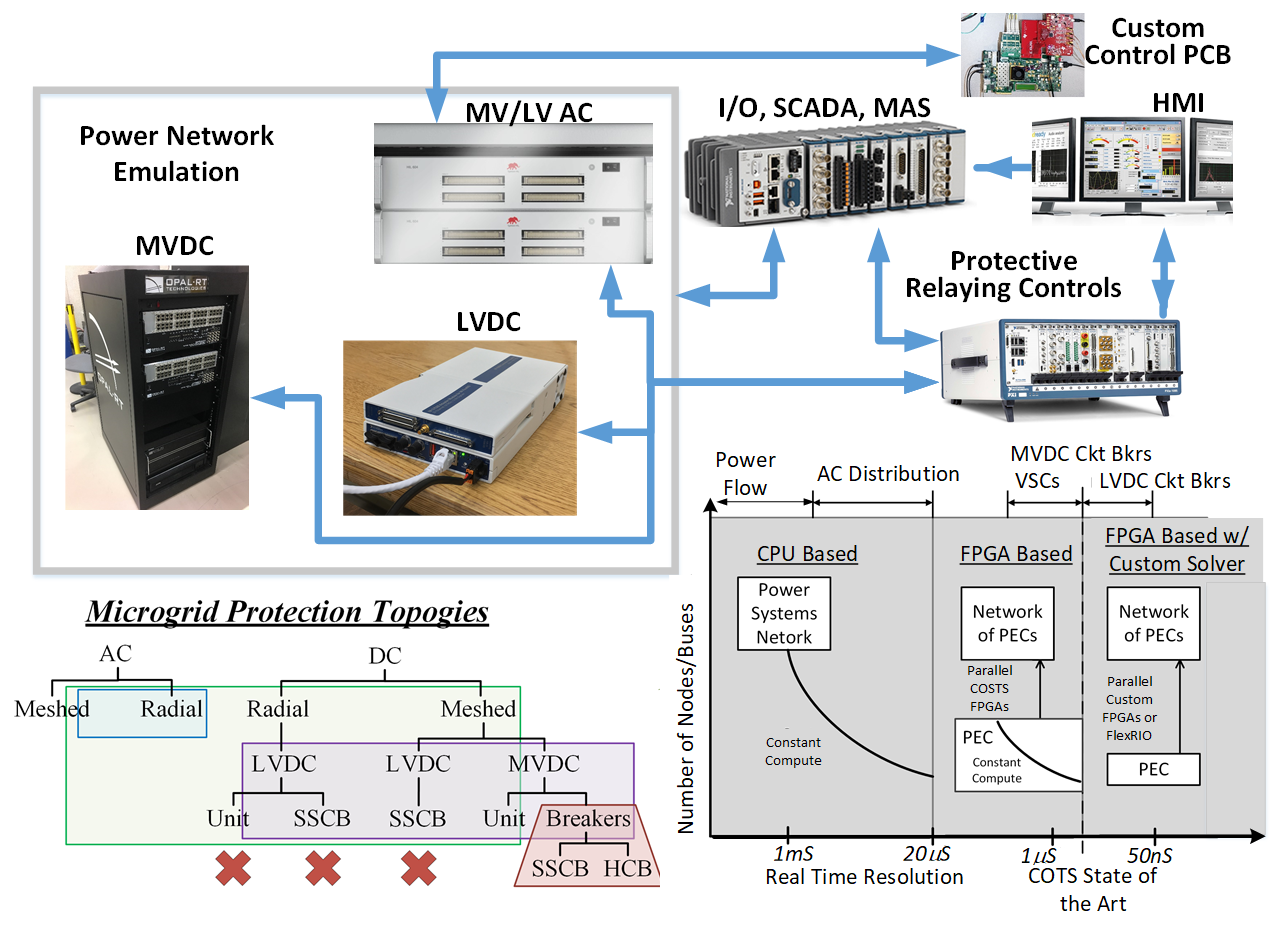

This project is a collaborative effort between UWM (Cuzner) and USC (Ginn, Benigni) to develop Hardware in the Loop (HiL) and Power Hardware in the Loop (PHiL) test platforms to develop protective relaying approaches for AC, DC and hybrid AC/DC microgrids. Presently, UWM has developed a Controller-Hardware in the Loop (CHiL) system that enables the study of timing propagation delays between distributed controllers embedded within Distributed Energy Resources (DERs), reliability of a decentralized microgrid control architecture and demonstration of scalability concepts. The UWM CHiL consists of Compact RIO units used to collect feedback information and interface with a Tertiary controller implemented in LabView. USC has developed an Integrated Grids Laboratory (InteGraL) that supports combined simulation of power and communication grids for testing distributed solutions for control and monitoring in distribution grids. The InteGraL system uses OPAL RT for power system simulation, NS3-RT and Apposite N-91 for communication network emulation, Compact RIO to emulate distributed control and data collection interfaces and multi-purpose ARM based processors to augment the HiL real-time simulation capability, 10Gbit communication between nodes is available. The plan is to augment the CHiL and PHiL systems at UWM and USC to add high speed serial communications for protective relaying. Common FPGA-based high speed serial communications implementations will be incorporated into the communication network emulations in order to research distributed and centralized schemes for achieving fault discrimination within the microgrid and to develop self-healing systems having autonomous fault detection, isolation and reconfiguration capabilities. This effort is part of a wider vision to enable collaborative research encompassing all levels of microgrid systems control and application to various industries.

Multi-Platform Controller Hardware-in-the-Loop emulation of microgrids for fault characterization and protective relay system evaluation

Recent Comments